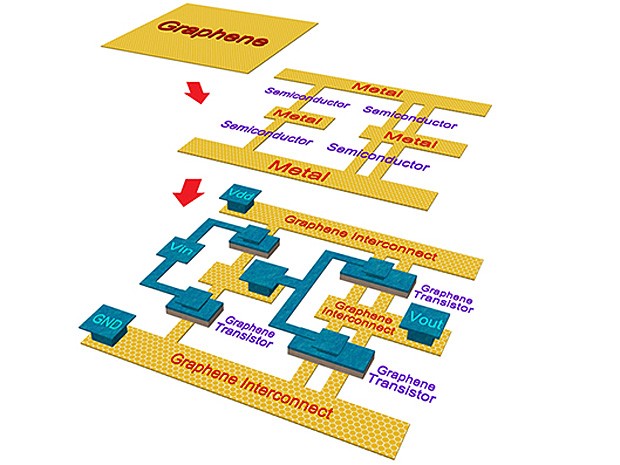

Il grafene è uno dei materiali che potrebbero sostituire il silicio nei chip del futuro. Circa due anni fa, IBM aveva dimostrato la possibilità di realizzare circuiti integrati in grafene, ma in quell’occasione era stato utilizzato un wafer di silicio e connessioni metalliche. I ricercatori del Nanoelectronics Research Lab alla University of California, Santa Barbara, hanno invece mostrato il design di un circuito ottenuto interamente da un singolo foglio di grafene.

I materiali comunemente utilizzati per realizzare i transistor CMOS e le interconnessioni pongono dei limiti alla miniaturizzazione dei componenti, in quanto la riduzione delle dimensioni causa l’aumento delle resistenze di contatto, una degradazione delle prestazioni e un aumento dei consumi. L’International Technology Roadmap for Semiconductors (ITRS) prevede che dal 2015 non sarà più possibile usare il rame per le connessioni, quindi è necessario trovare al più presto una soluzione alternativa. Il circuito integrato progettato dall’università californiana (un inverter a due stadi) usa invece transistor e interconnessioni in grafene.

Kaustav Banerjee, direttore del Nanoelectronics Research Lab, ha evidenziato un’altra interessante proprietà del materiale. Il grafene possiede una “tunable band gap“, per cui è possibile modificare la larghezza delle strisce tramite la litografia per trasformarlo in semiconduttore o in metallo. Inoltre, strisce contigue permettono di progettare componenti attivi e passivi con basse resistenze di contatto.

La ricerca, pubblicata sulla rivista Applied Physics Letters, ha permesso di dimostrare che un circuito “all-grafene” ha un margine di rumore 1,7 volte maggiore e un consumo 1-2 decadi inferiori rispetto alla tradizionale tecnologia CMOS. Al momento si tratta solo di un design, ma i ricercatori affermano che le prestazioni di un eventuale processore basato su questo progetto sono superiori a quelle di un chip CMOS a 22 nanometri.

/https://www.webnews.it/app/uploads/2013/03/Grafene.jpg)

/https://www.webnews.it/app/uploads/2024/10/ffbff933-17df-478e-9d1f-5503d03605bf.jpg)

/https://www.webnews.it/app/uploads/2024/10/357278.jpg)

/https://www.webnews.it/app/uploads/2024/10/28ebc471-1da5-41bb-b544-e96651c3f5ac.jpg)

/https://www.webnews.it/app/uploads/2024/10/image-1600-bbe4e7f39d32abd052f3f51785442db4.jpg)